# 16K Memory for \$360

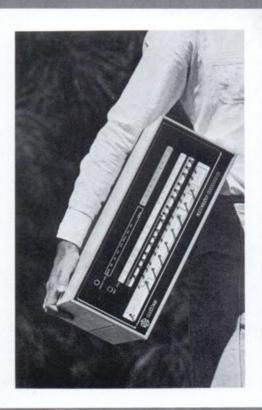

Unbelievable, but true - a 16K dynamic memory board breaking the \$400 barrier. And who would you most expect it from but MITS.

The Altair 88-16MCD offers many outstanding features at a price usually associated with budget products. To begin with, the 88-16MCD can be used in any Altair Bus computer with full compatibility. All refresh circuitry is located on the PC board and receives timing pulses from the CPU, Logic

synchronization is crystal-controlled an continuous (no wait states). As with all N plug-in boards, the 88-16MCD consu es little power (2.5 watts) and is accessed quickly (RAM access is 350 nanoseconds).

Memory expansion is no longer an expensive proposition when adding the Altair 88-16K Dynamic Memory Board. Build it yourself for \$360," or let us do the honors at \$395\* Either way, it's the best deal in town.

miss

a subsidiary of Pertec Computer Corp. 2450 Alamo S.E. Albuquerque, New Mexico 87106 (505) 243-7821

\*Prices may vary depending on dealer location

# SUBMITTAL SPECIFICATIONS

Articles submitted to Computer Notes should be typed, double-space, with the author's name, address and the date in the upper left-hand corner of each numbered page. Authors should also include a one-sentence autobiographical statement about their job, professional title, previous electronic and/or computer experience under the article's title. Authors should retain a copy of each article submitted

All illustrations, diagrams, schematics and other graphic material should be submitted in black ink on smooth white paper. Prints and PMT's are acceptable. No pencil draw- ribbon possible on blank white paper. A paper tape for ings unless properly "fixed." No halftone or wash drawings. each program submitted must also be included.

All artwork should be mailed flat, never folded. Unless requested, graphics are not returned. Sketches, roughs and "idea" drawings are generally not used.

Photos, charts, programs and figures should be clearly labelled and referred to by number within the text of the manuscript.

Only clear, glossy black and white photos (no Polaroid pictures) will be accepted. Photos should be taken with uniform lighting and sharp focus.

Program listings should be recorded with the darkest

COMPUTER NOTES is published monthly by MITS, Inc., 2450 Alamo SE, Albuquerque, NM, 87106, (505) 243-7821. A free year's subscription is included with every purchase of an Altair™ computer. Regular subscriptions can be ordered from the MITS Customer Service Dept. for \$5 per year in the U.S. and \$20 per year for overseas. Single copies are available for 50¢ each at all Altair Computer Centers. Entire contents copyright, 1977, MITS, Inc. Send articles, questions, comments and suggestions to Editor, COMPUTER NOTES, MITS, Inc.

MITS, Inc. 1977 (Volume 3, Issue 4, September, 1977) a subsidiary of Pertec Computer Corporation 2450 Alamo S.E., Albuquerque, New Mexico 87106

Altair is a trademark of Pertec Computer Corporation

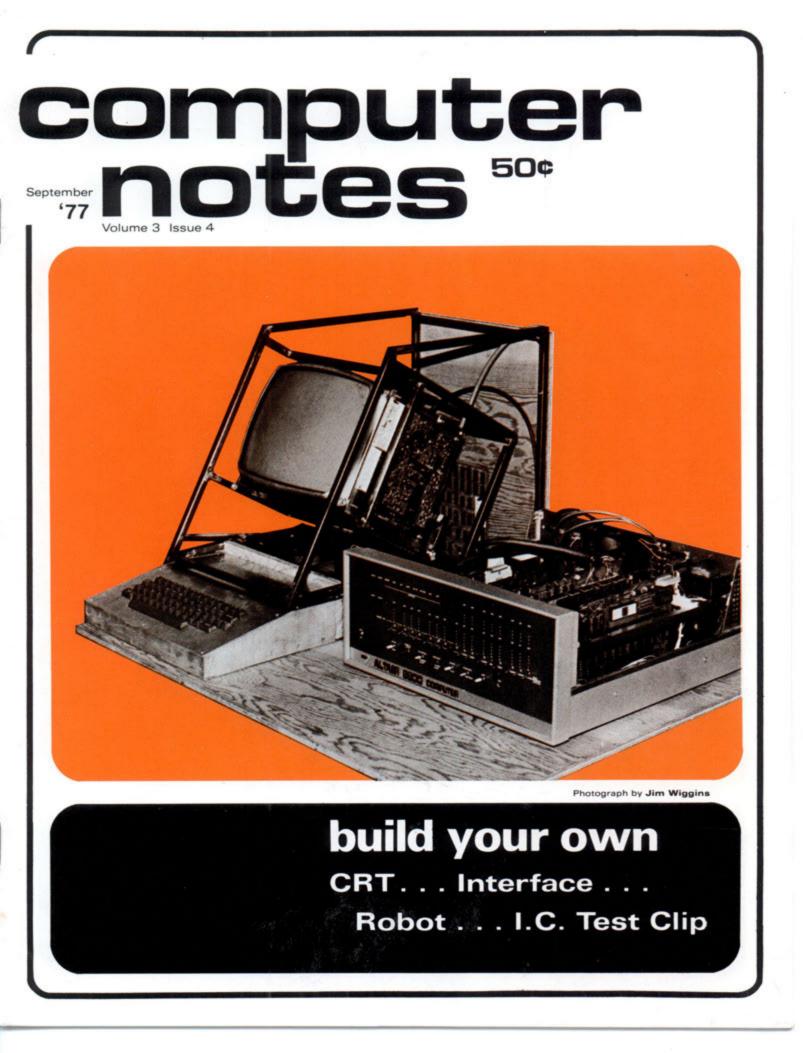

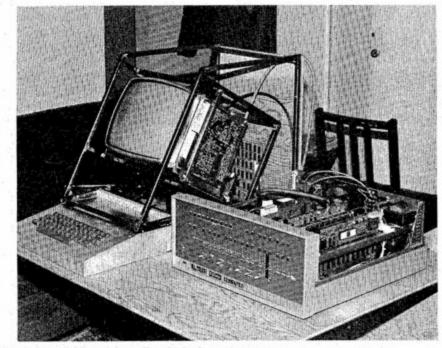

# NEED AN INEXPENSIVE CRT? Build One Using an Altair 8800-Compatible Interface Card

By Jim Wiggins 400 Pemberton Terrace #116 Kamloops, B.C. Canada V2C 1T3

Wiggins is an avid microcomputer hobbyist who plans to return to school to make computers his vocation.

The CRT terminal and the floppy disc system currently seem to be the most desirable peripherals for microcomputer users. However, they are also the most expensive and for this reason the literature is replete with techniques for hobbyists to inexpensively built or buy their own. The following article describes how a relatively inexpensive, high-quality CRT terminal can be constructed using a commercial Video Ram (VRAM) and an Altair 8800 compatible interface card.

> The heart of the terminal is the VRAM (\$390), which is manufactured by: Matrox Electronic Systems P.O. Box 56, Ahuntsic Stn. Montreal, Quebec Canada, H3L 3N5 The cord itself, which unfortunately

The card itself, which unfortunately will not fit inside the Altair Computer case, consists of 2K of memory for a display of 24 lines of 80 characters per line with each

character being displayed in a  $7 \times 9$  dot matrix format. The character set used in the standard MTX 2480A is the 128 character ASCII+Greek. Custom designed as well as several other standard character fonts are also available. Because the required video signal is generated from the on-card memory, DMA is not required, and the card is read from and written into as if it were normal processor memory.

Although the card contains 2K of memory, it appears as 4K on the address bus. This is due to the address decoding scheme. (See Fig. 1). Address lines A6 to A0 inclusive access columns 0 to 79, and address lines A7 to A11 access lines 0 to 23, while column addresses 80 to 127 and line addresses 24 to 31 are ignored. In a sense, this wastes memory address space, continued

#### EDITOR Andrea Lewis

ASSISTANT EDITOR

PRODUCTION Al McCahon Steve Wedeen Beverly Gallegos Lucy Ginley

#### CONTRIBUTORS

Dave Antreasian Bruce Fowler James A. Gupton, Jr. Robert Rossum Mike Smith Jim Wiggins

MITS, Inc. 1977 a subsidiary of Pertec Computer Corporation 2450 Alamo S.E. Albuquerque, New Mexico 87106

### IN THIS ISSUE

| Need an Inexpensive CRT?                            | . 1 |

|-----------------------------------------------------|-----|

| Careful Bull in the China Shop                      | 4   |

| Build Your Own Interface                            | . 8 |

| Students Develop IC Logic Test Clip for Altair 680b | 15  |

| What's Microcomputer Class Without an Altair 8800b  | 16  |

| Programmable I/O Made Possible With the PIA         | 18  |

| Glitches: Troubleshooting the 88-4PIO               | 20  |

### NEED AN INEXPENSIVE CRT?

#### continued

but it isn't a real concern unless you have 62K memory.

Another important feature of the card is the data bus, which is bidirectional and 9 bits wide. Bits 0 through 6 comprise the character code, and bits 7 and 8 are used to select one of four display modes (for each character): normal (00), half intensity (10), inverse video (01), and blink at 1 Hz rate (11). In order to simplify the interface card, I have tied bits 7 and 8 together so that characters are either normal or blinking. However, other combinations, such as normal/inverse or inverse/blink, can be obtained quite easily.

In addition to the address and data lines, there are several other input and output lines from the VRAM used by the display monitor and the interface card. Since both the composite (logic plus sync) and the logical video signals as well as the horizontal and vertical blanking pulses are available, there are only a few restrictions on the type of monitor used. One restriction is that the monitor must have a bandwidth of 10 Mhz minimum. It must also have a long persistance phosphor if the 128 character set fonts are used. The one 64 character font ( $5 \times 7$  dot matrix), upper case ASCII, is the exception to this in that a monitor with a standard phophor may be used. For readability, Matrox recommends that the monitor be 12 inches or larger. The vertical blanking (BV) from the VRAM is also used by the interface card as a status signal to control access to the VRAM card itself.

Although the VRAM may be read from or written into during the beam trace time, a noticeable flicker results. For this reason, the BV signal and the interface card ensure that access to the card is during vertical retrace (4.61 msec). The chip select  $(\overline{CS})$ , which is active low for read and write, and read/write (R/W), which is active low for write, are the only control signals from the interface card to the VRAM required for operation. Although the actual timing relationships are not shown here, they are similar to those for the memory chips themselves, i.e. 2102-1. The minimum read and write cycle times for these chips are 500 ns, which makes it technically possible to access VRAM without memory wait states. However, because the VRAM is separated from the interface card by six feet of ribbon cable, two wait states are used to ensure that data is stable during the write pulse or the processor read pulse DBIN.

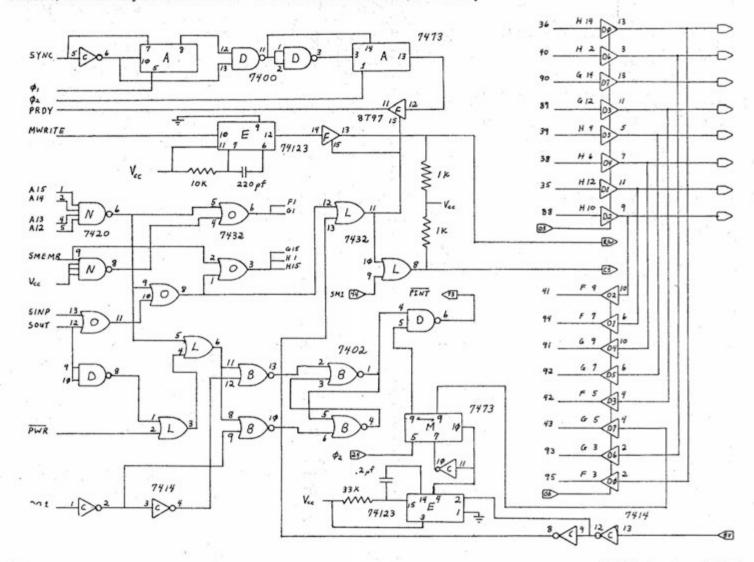

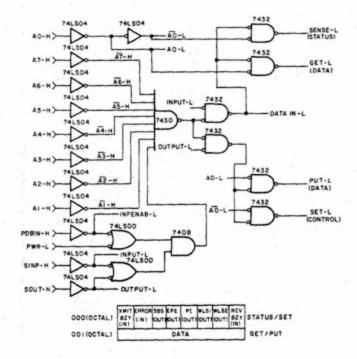

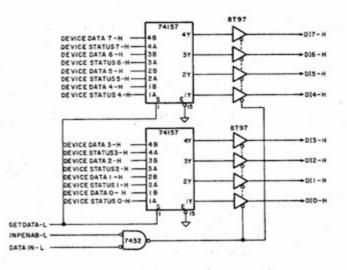

The interface card itself is shown in Figure 2 with IC A used to request the required wait states. Before examining the circuit, I would like to thank MITS for their indirect assistance in the design of this interface card. Owners of the MITS 1K Static and S10B cards will note a distinct resemblance in the decoding, wait state generation, and interrupt enable circuitry.

CN/September, 1977

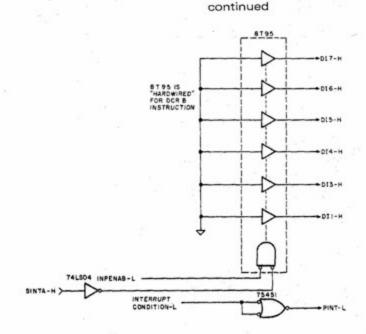

(Apart from these areas of similarity, the design is all mine; patents are pending.) Not shown on the schematic of Figure 2 are 2 hex buffers for the 12 address lines and pull-up resistors on the 8 data lines. While the Altair computer uses separate input and output busses, the VRAM uses a bidirectional bus which is split, using 8T97s, ICs, F, G, and H. Four gates of F and 4 of G comprise the data in, and 6 of H and 2 of G are used for data out. To the left of the schematic, the ICs N and 0 select either the data out or data in lines, depending on the states of SOUT, SIMP, SMEMR and, of course, the address lines A12 to A15 (IC N6). DI is selected through IC 0 pin 6, and DO is selected through IC 0 pin 3. IC 0 pin 8 is active low during both read and write operations. It is this signal applied to IC L pin 12 plus the BV signal applied to IC L pin 13 that produces the chip select (CS) pulse at IC L pin 8. CS is also, possibly unnecessarily, a function of M1, because IC 0 8 will go low during the latter part of M1. IC L pin 11 also enables two gates of IC F via pin 15 of F. The R/W signal is applied through one to the VRAM, and the other is the source of the PRDY signal to the processor.

There's also output port on the interface card. It's used for interrupt enable, which consists of the RS flip-flop comprised of the 4 gates of IC B. Data on the D01 line sets or resets this FF, and the effective write pulse for the port is generated when IC L pin 6 goes low. The output at IC L pin 6 is a function of PWR (IC L 2), SOUT (IC D 9), and the port address applied to pins, 1, 2, 4, and 5 of IC N. In this situation, it is the 4 most significant bits of the port address (which appears on both the upper and lower halves of the address bus) that cause the port to be selected. IC N 6 thus performs the dual purpose of selecting the output port as well as the memory space of the VRAM. This scheme does restrict users to 240D output ports, but that should be more than sufficient. The execution of the instruction OUT 350 will, therefore, set or reset the FF, the output of which is applied to enable the interrupt gate at pin 4 of IC D. The signal that produces the interrupt is a function of the BV and is generated by IC E and M. The period of retrace is 4.61 msec. which is shortened to about 3.5 msec by IC E and is synchronized with phase 2 by ICM. The output of ICM at pin 9, which is active high, thus generated the interrupt at IC D 6 during retrace. This signal is also

fed to IC G 4, DI7, where it can be monitored by such memory reference instructions as MOV, A and M.

The pulse at IC M 9 is shorter than BV, so D17 can be sampled during the final microseconds of that pulse. In that case, when the card is accessed, even though IC M 9 is low, IC L 13 will still be active low, and the CS pulse can still occur.

The following program briefly illustrates the method of operation. The program simply fills the screen with a given character and loops. 00 MVI

| 00 | MVI     | 076 | Set accum with desired character                      |

|----|---------|-----|-------------------------------------------------------|

| 01 | DATA    | 067 | ASCII 7                                               |

| 02 | STA     | 062 | Store accum                                           |

| 03 | L       | 100 |                                                       |

| 04 | н       | 003 |                                                       |

| 05 | LXI     | 001 | Set reg pair B with line increment                    |

| 06 | C       | 200 | this is one in bit 7                                  |

| 07 | В       | 000 |                                                       |

| 10 | LXI     | 041 | Set reg pair H with starting address of display       |

| 11 | L -     | 000 |                                                       |

| 12 | н       | 360 |                                                       |

| 13 | MOV A,M | 176 | Move data byte form interface card to accum           |

| 14 | ANI     | 346 | Clear off everything but bit 7-retrace status         |

| 15 | DATA    | 200 |                                                       |

| 16 | JZ      | 312 | If zero not in retrace, so loop till retrace          |

| 17 | L       | 013 |                                                       |

| 20 | H       | 001 |                                                       |

| 21 | LDA     | 072 | As in retrace, load accum with data                   |

| 22 | L       | 100 |                                                       |

| 23 | н       | 003 |                                                       |

| 24 | MOV M,A | 167 | Move accum to VRAM                                    |

|    | INX     | 043 | Increment column/line counter in reg pair H           |

| 26 | MOV A.L | 175 | Move reg L to accum-contains column count             |

| 27 | ANI     | 346 | Clear off bit 7, which is part of line count          |

| 30 | DATA    | 177 |                                                       |

| 31 | CPI     | 376 | Compare column count with 80D-last plus one of column |

| 32 | DATA    | 120 |                                                       |

| 33 | JNZ     | 302 | If not zero, then more on line to go                  |

| 34 | L       | 013 | · · · · · · · · · · · · · · · · · · ·                 |

| 35 | н       | 001 |                                                       |

| 36 | MOV A.L | 175 | Line completed, so column count in L to accum         |

| 37 | ANI     | 346 | Clear off all but bit 7, which is part of line count  |

| 40 | DATA    | 200 |                                                       |

| 41 | MOV L,A | 157 | Move cleared column count back to L                   |

|    | DAD     | 011 | Increment line count by double add with reg pair B    |

| 43 | MOV A,H | 174 | Move line part of address in H to accum               |

|    | CPI     | 376 | Compare with last line plus one                       |

| 45 | DATA    | 374 | This is 360Q plus 140, which corresponds to line 24D  |

| 46 | JNZ     | 302 | If not zero, then more lines to go                    |

| 47 | L       | 013 |                                                       |

|    | Ĥ       | 001 |                                                       |

|    | JMP     | 303 | Screen filled so loop                                 |

| 52 |         | 000 |                                                       |

|    | Ĥ.      | 001 | - A                                                   |

|    |         |     |                                                       |

This combination of Matrox 2480 with the Altair 8800 compatible interface card has resulted in an excellent but relatively inexpensive CRT terminal. Although I used a separate interface card (partially because of impatience), other users may not have to, since Matrox has been working on a card compatible with Altair computers and may now be producing it.

The benefit of a separate interface card (apart from space considerations) is the freedom in being able to choose the aspects of the interface which are the most important, as I have done with the interrupts and bits 7 and 8. Requirements will differ among people, and some may, for example, decide to access VRAM during horizontal retrace, which would about treble the data transfer rate. Using vertical retrace, the data rate is about 6000 characters per second; using horizontal retrace, rates of 18000 characters per second and greater could be achieved. As another example, latches could be implemented to use the full 9-bit data bus for reading and writing. The interface card described here, while more than adequate for my purposes, is therefore only one of many possible ways of building a viable CRT terminal with the Matrox VRAM.

# CAREFUL BULL IN THE CHINA SHOP A Cheap Approach to the Mechanics of Robotics

This is the first article in a three-part series on building a robot. Part II will cover in detail the mechanics of robot building, and Part III will discuss applications.

Members of the United States Robotics Society (USRS) are using the family name "Rossum" as a kind of collective pseudonym for their publications. Members who prefer to be anonymous may publish through USRS under whatever "Rossum© USRS

name" they reserve. Thus far, half a dozen names have been spoken for, e.g. "S.A. Rossum," "D.I. Rossum," and some folks whose real family name is Rossum have been listed.

"Robert Rossum" is a writer of books, articles, and non-theatrical motion pictures, who has spent most of the past 20 years working in research and developmental laboratories.

#### Part I

#### By Robert Rossum

Someone once said that the most interesting thing computers ever do is to blow hot air on your shoes while they hum and soak up money. An intelligent machine, no matter how clever, lacks charm if it just sits around like a bump on a log. Perhaps part of the current enthusiasm for robotics is a reaction to this static performance of our clever machines. Roboticists almost universally report their determination to construct mobile systems.

The ordinary roboticist is usually a good thinker-upper, programmer, planner, and innovator but seldom a first-rate mechanical engineer and master machinist. Although drawing conceptual plans for experimental mechanical systems is a necessary first step, actual construction and modification of mechanical creatures is prohibitively expensive in cash and time. The mobile systems built by institutions and private workers tend to be awkward. fragile, unstable, and uninteresting as well as expensive. The interesting machines that receive national publicity tend to be anthropomorphic monsters. One such recently publicized system is over six feet high and weighs several hundred pounds. It performs some remarkable tricks under the remote control of its master but looks mighty unstable on its small base. Watching it causes the uneasy feeling that if it dropped a wheel off the edge of a walkway, it would topple over, crushing dog, child, mailman, or Volkswagen. The publicity arising from that incident might not bring cheer to other roboticists.

Even the cute little wheeled systems that experimenters set to snuffling around their laboratories have no more athletic prowness than is required to climb over a doorsill or up on a rug without stalling or upsetting. Conventional mechanical systems are generally proving unsatisfactory for devices that are intended to simulate the performance of living things.

The flaw in the simulation is not chiefly the lack of intelligence. David Heiserman, author of BUILD YOUR OWN WORKING ROBOT, has observed that his robots acquire behavioral characteristics of living creatures, responding to their environment in a surprisingly complex fashion. In his book, Heiserman said the fact that impresses him most is the simplicity of the circuitry involved. He said a few basic sensory channels, simple reflexes, and a trifle of logic allow his machines to behave like simple animals. It may be that the devices are intellectually trivial, but since they can move, displaying their characteristics overtly, and can alter their performance in response to a changing environment, they are interesting. Heiserman's mechanical systems are quite crude, but at least they do something.

If experimenters today can develop cheap and dirty mechanical systems that any clumsy amateur can build in his own garage, the progress in robotics will be significant in the next few years. The purpose of this series is to briefly describe a cheap, not inexpensive, but **cheap** mechanism for many robotics applications. No detailed designs are offered, but roboticists will be able to use the basic principles of the system without further elaboration here in print.

In this electronic age, we think of

robotics mechanisms in terms of electronically-controlled servosystems, stepping motors, and complicated, heavy gear trains. Consider servos. Since no mechanical system if perfectly accurate, we must always provide a trial-and-error system that will let a free-moving device accomplish its tasks in spite of imperfection. For example, if you set your pet robot on a course for a fire hydrant a block away, you can be sure that the critter will miss the fireplug unless it knows one when it sees one and can hunt around as necessary to find the thing. Just aiming straight from where you are to the hydrant won't work, since irregularities in the pavement, uneven wear in the robot's wheels and gears, bad aim, or a dozen other problems will almost inevitably prevent the machine from going directly from one place to the other. The robot must be able to correct its course, to "zero in" on the target. Of course, when the machine changes its course, the correction is not likely to be prefect. It may over-correct or encounter more problems along the way. Ordinarily, a servomechanism is employed to make up for imperfections in the rest of a machine, to make the back-and-forth corrections necessary to guide or position a machine properly. The servo is precise in that it takes the machine to exactly the right position. But it's not necessarily "accurate," since it doesn't follow a detailed set of instructions to get to a target.

The distinction between precision and accuracy is important. If your robot is accurate, you may give it instructions such as: Move exactly north 315 feet and five inches. Then make a 90° turn to the left (not an 89 turn or a 91 turn but a 90 turn), and move exactly 19 feet and seven inches. Stop there, or you'll smash your little lens on the knobby thing that is sticking out of the hydrant.

What are the chances that you really know exactly what the instructions should be and that your robot can carry them well out enough to get within six inches of the hydrant? Not very good, unless you have an uncommonly well-made, expensive machine (equipped with a magnificent inertial guidance system, perhaps) working in an environment without obstructions. If there are cracks in the sidewalk, you're in trouble.

If your robot is equipped with sensors and servos, it can use instructions more like this: Move along the sidewalk to the north without falling off the edge or bumping signposts until you detect something that looks like a fireplug off to the left, about 300 feet along the way. Then move toward that hydrant until you're six inches from it. Stop there.

Chances are good that the robot will go precisely where you want it to go. That's precision, not accuracy. The robot may be constructed with only lousy components, may not be able to run accurately within five degrees, may be off by three percent in its judgment of distance, but it will do what you want it to do. Remember that living things are built entirely of lousy, individually unreliable, and irregular components. Even the brain is constructed of stuff that couldn't meet military specifications for purchasing, regardless of actual performance.

Remember, too, that when an animal lifts its foot, it does not usually have to swing that foot clear around a 360 arc to return it to its starting position. Feet move forward and back, up, and down. Tails move to and fro. Muscles in living creatures are paired. Your bicep pulls your forearm up, and your tricep pulls it back Mechanical servomechanisms down. usually work with paried motors, pulling things first one way, then the other, "zeroing-in." The builder is usually depressed by the realization that almost everything in his critter must be duplicated --all motors matched or at least reversible. One common ploy is to make the motor pull against a spring that returns a limb to "normal" position after the motor moves it.

Robot designers usually provide a motor for an arm, a motor for a head, a motor for wagging the tail, etc. or very complex, heavy, power-consuming gear systems to accomplish all these functions with a single motor. But let's consider an alternative -- the ancient double windlass

CN/September, 1977

mechanism. Its virtues for the roboticist are many. (See any encyclopedia; look under "captain.")

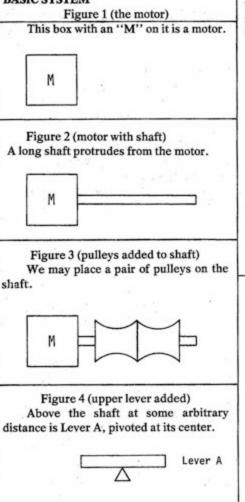

#### BASIC SYSTEM

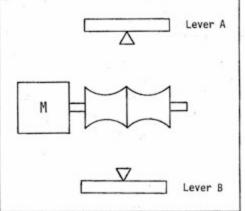

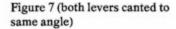

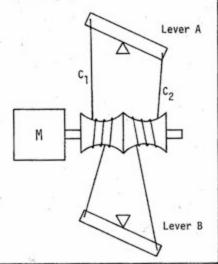

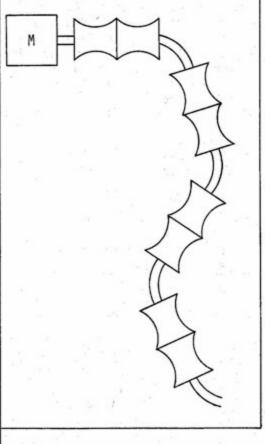

Figure 5 (lower lever added) Below the shaft is Lever B, also pivoted at its midpoint. Our interest here is in getting Lever B to do something in particular when we move Lever A.

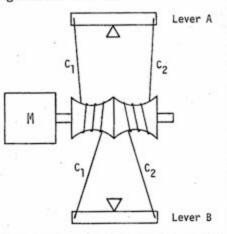

Figure 6 (Cords C1 and C2 added)

We connect Levers A and B with Cords C1 and C2. The cords are wrapped loosely around the pulleys on the shaft so that when the motor turns the pulleys just spin inside the loose cords without affecting them and the levers.

Suppose that you take hold of Lever A, tilting it upward at the left end. That pulls Cord C1 tight around its pulley, but Cord C2 remains loose around its pulley. Here the mechanical magic begins. As Cord C1 grips the pulley, the force of the motor begins to pull on the cord. Even if you lift the end of the lever very delicately with your fingertips, the cord, hence also the end of Lever B, will be pulled by the full force of the motor. You need only keep a bit of tension on the top part of that cord to apply the motor's full force to the task of lifting up the end of Lever B.

If you pull the end of Lever A steadily up to some particular position, the motor will wind up the lower part of Cord C1 until Lever B is cocked at the same angle as Lever A. Then the cord will begin to slip on

continued

### CAREFUL BULL IN THE CHINA SHOP

the pulley, and the pulling force of the motor will be relieved. You have applied a small control force to the upper lever, causing the motor's force to be applied to the lower lever. In fact, a weight of some significance might be hanging from that left end of Lever B.

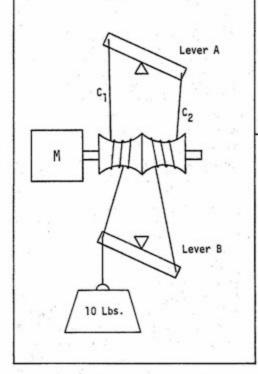

#### Figure 8 (10 lb. weight hanging from Lever B)

This is far more weight than you could lift with your fingertip. The motor would do the lifting, multiplying the control force greatly.

Notice that when the Cord C1 begins to slip, C2 is just on the point of growing tight. When the action stops, the windings of the two pulleys are slightly loose, just as they were when the action began. The system is all ready to perform again promptly when another control force is applied to a lever. If you pull up on the right end of Lever A now, Lever B will be returned to its original matching position -sort of a bicep-tricep action.

You've done two things -- controlled the position of Lever B by manipulating Lever A and multiplied the tiny control force with the force of the motor. These are both very important to the roboticist who is hoping to control the limbs of a mechanical creature.

#### SOME MORE BASICS

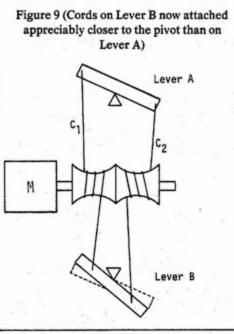

You may choose to amplify your motion as well as your control force. continued

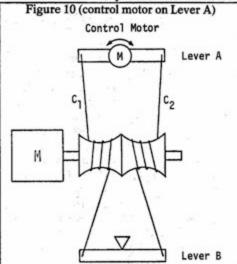

In fact, your control motor might sensibly by a reversible shaded-pole motor. Motor experts say that a shadedpole motor can be held in a stalled condition indefinitely without damage, and that's an advantage. (As later article will discuss a mixed bag of alternative to control motors.) With signals from your robot's brain, presumably your personal computer, you can move Lever B either way automatically with appreciable force.

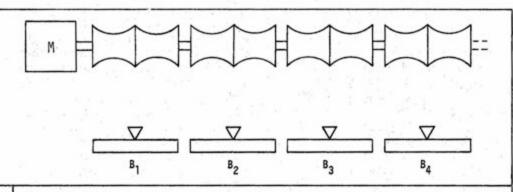

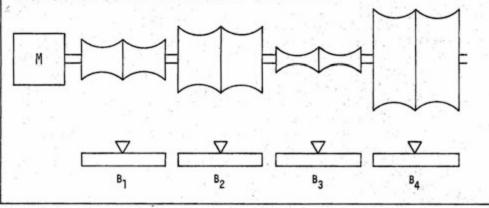

### Figure 11 (main motor shaft with more sets of pulleys)

The shaft from the main motor may be equipped with numerous pairs of pulleys so that power may be applied at any point along the shaft to any chosen lever down below.

If you now raise the left end of Lever A the same distance you did before, the force of the motor will be applied to Lever B in the same way. The same length of cord will be drawn up by the pulley, but the left end of Lever B will be moved a greater distance. You have multiplied both force and motion.

The motor here may be as large as you like, depending upon the application. The control force you apply to Lever A may, in fact, be supplied by another motor, since your robot will probably employ an electrical system, and turning power off and on in electrical motors will be a straightforward matter. The control motor may be small, both in physical size and power. (The main motor may even be gasoline or steam powered, if you like, depending on your application and willingness for your robot to breathe real smoke and fire with a variety of associated noises.

Figure 12 (flexible shaft with pulleys along its snaking path)

The shaft may be flexible so that power can be transmitted from the main motor to remote regions of the robot in which it resides.

Figure 13 (various sizes of pulleys on the shaft)

All the pulleys may be of different sizes on this same shaft so that Lever B1 may be moved with a different amount of power from that applied to B2 and so on. Maybe you don't want the robot to wag its tail with enough force and speed to smash a chair leg. You can control the speed and power of the way by choosing levers of appropriate length and pulleys of appropriate diameter.

An important consideration at this point is shared power. Obviously, there's a limit to the number of pulleys you can put on the shaft of a given motor. There's a practical physical constraint of some kind to balance your every wish. If you tighten the cords at every point along the shaft. drawing power from the motor at each pair of pulleys, your chances of overloading the motor are very great. But there's the beauty of the system (well, one beauty among many) -- it works like an animal. Like any animal, you rarely use all of your muscles at once. When you run, you may be using your leg muscles in an extreme fashion, but you are not simultaneously using your neck and arm muscles to their fullest extent. Chances are that you are not also trying to bite through a heavy

bone, too, drawing a great deal of energy in your jaw muscles.

That's a very significant factor in the design of animals. You have a certain amount of chemical energy stored locally in vour muscles. When you move the muscles, you consume some of that available energy. If you exert the muscles greatly, you use up all that's available locally, and must get more sugar from the liver. With great exertion you can develop a severe shortage of energy locally. Luckily, you seldom exert all muscles at the same time, so you don't develop a general deficit of energy. (However, people do sometimes die of overexertion. That's one of the problems for people stuck in blizzards. They tend to use up all of their reserves struggling through the snow, and

then lie down to rest. When they quit moving, they quit pumping new chemicals to their depleted muscles fast enough. The cold and lack of energy may be fatal.) The analogy is not perfect, but it's pretty good. This double windlass system allows the energy of the main motor to be shared by many functions in the body of the robot. The average load on the motor can be quite low, while large amounts of energy are rapidly available wherever needed. When separate motors are used at all places where energy is needed, those motors must be big enough to supply all the energy that will ever be needed from them. That means a lot of extra weight is being dragged around all the time just in case a burst of energy is needed. The double windlass system solves much of this problem with a comparatively simple simulation of the system Nature has been using effectively for a long time.

I'm not complaining about standard mechanical systems. There's much to be said for the clever designs that competent engineers have developed for robotic and non-robotic mobile systems using modern technology. However, cheapness is not a feature of standard mechanical systems, and the average home craftsman simply can't cope with them.

The double windlass system can be assembled by the home experimenter with Tinkertoys or an Erector Set. The interested roboticist can work with this system himself even before the next article in this series on more mechanics of robotbuilding is published next month.

The pulleys can be empty thread spools in the experimental system. When you get around to building a rig that's meant to last, you'll want to use metal, because there's a lot of wear. Don't the cords stretch? Sure, and they'll have to be tightened once in a while. So what? At least you can figure out what's wrong and fix it yourself. (And there will be many maddening problems inherent in this system as in any other.) By machinists standards, the whole mechanism can be quite sloppy and still work. Precision can be achieved in a sloppy system without accuracy.

In the discussions leading up to this article someone asked: "Isn't there a real safety factor in the fact that the cords will slip on the pulleys if they are overloaded?"

"Oh, no. The cords will break before they slip. This is the kind of mechanism people use to pull two or three miles of oil drill stem up out of wells. The windlass is a powerful tool. Why do you ask?"

"Well, I guess I don't want the robot to be too strong."

> continued Seven

# BUILD YOUR OWN INTERFACE Tips from a professional

#### By Mike Smith

Smith is a professional design engineer and avid computer hobbyist. His article deals with Altair bus signals and three different types of I/O: Flag Testing, Program Interrupt, and Direct Memory Access. This story first appeared in the June 1977 issue of KILOBAUD. Copyright 1977 KILOBAUD Publications, Inc., Peterborough, NH, USA. All rights reserved. Reprinted by permission.

One of the most interesting and rewarding areas of the personal computer hobby is that of designing and building custom interfaces. Aside from the sheer pleasure and satisfaction that comes with seeing your new design work, there is the possibility of interfacing something that has never been interfaced as well as the benefit of substantial money savings as compared to the purchase of a commercial kit or finished product.

This article deals specifically with interfacing to the Altair 8800 series of

### CAREFUL BULL IN THE CHINA SHOP

continued

"Too strong for what?"

"For people. I don't want it to hurt anybody by accident, and I though maybe the cords would slip in case the machine happened to be gripping somebody too hard."

"Ah. Well, you'll have to take care of that in the machine's logic. I suppose you could build in a sensing circuit that makes it turn off when it hears a scream."

"That isn't the comfort I was looking for."

"Sorry. A machine is a machine. Build it the way you want to build it. Maybe it can learn to be careful."

I haven't discussed the logic, brain, or reflexes of a robot in this article, though some of those matters will be touched upon later in the series. Instead, I've offered a cheap and dirty approach to making robots **do** something interesting. If you have been stewing in frustration over your inability -financial or mental -- to build a working system to go with the brains on your shelf, get busy with the spools and Erector Set motors. computers and applies equally to all three models (8800, 8800A, and 8800B). The first step toward successfully interfacing any computer is a thorough understanding of the bus. The Altair Bus is a 100 line printed circuit board bus, in which all like numbered connector pins connect to one another via etched copper lines. This structure allows any interface, CPU or memory printed circuit board to be inserted into any vacant connector slot. The 8800A and 8800B come equipped with an 18-slot bus (mother board), while the 8800 is provided with a 4-slot bus with space provided for 3 additional 4-slot mother boards.

Each of the 100 lines on the Altair Bus has a predefined function which must be fully understood in order to make good use of the bus.

Table 1 contains a complete breakdown of all the Altair Bus signals, given in functional logic notation. This means that in each signal mnemonic there are two parts. The first is the signal abbreviation and the second is the active level representation. The two parts are separated by a hyphen for clarity. The active level representation is in the form of an upper case H for active high and an upper case L for active low. Functional representation does not apply to power and ground lines. To correlate the functional logic shown here to the "positive logic" symbology shown in the Altair documentation, drop the active level representation and draw a Boolean NOT sign over the tops of these signals shown here as L. The functional notation is a far better approach because it reserves the use of the Boolean NOT symbol for use when NOT is intended. Positive logic notation on the other hand, uses the NOT symbol every time an active low is indicated, so that every time the logical NOT function is desired, it will be confused with active low.

Let's take a look at the major groups of signals on the bus. The **address** lines are outputs from the CPU board and are inputs on all memory and I/O boards. The I/O boards use only the lower 8 bits (A0-H through A7-H) because during I/O transfers, the upper 8 bits are identical to the lower 8 bits. In the event that direct memory access (DMA) is used, the DMA controller must also generate an address

on the address lines. In the 8800 and 8800A, these lines (through current limiting resistors) provide the drive for the Address indicators on the front panel. This seriously limits the high going drive of the 8T97 drivers on the CPU board and therefore it is suggested that each board receive the address lines using only one low power TTL or low power Schottky TTL device. In the event that a DMA controller is being designed, it is recommended that address drivers equivalent to the 8T97s on the CPU board be used.

The data-out lines are outputs from the CPU board and are inputs on all memory and I/O boards. In the event that DMA is used, the DMA controller must also drive the data-out lines when the direction of the data transfer is to the memory from the DMA controller. Assuming no more than the 18 cards that will fit in the cabinet are connected to the bus, up to 2 milliamps of low loading may occur on each board in the bus. This equates to one standard or Schottky load, 5 low power Schottky loads, or 10 low power TTL loads. A DMA controller should drive these lines with 8T97 Tri-state buffers or equivalent.

The data-in lines are inputs to the CPU board and are driven from the memories and I/O boards. In the event that DMA is used, the DMA controller is an additional input for the data-in lines. Also, the front panel is an input for these lines. Since the front panel and CPU both use 74LS04 receivers for the data-in lines and the lines are "pulled-up" using 1k Ohm resistors at the CPU board, almost any Tri-state or open collector TTL driver may be used to drive the data-in lines from the memory and I/O boards. However, to insure optimum noise immunity and capacitive drive over the length of bus, it is recommended that the 8T97 type buffers be used to drive the data-in lines.

The status lines are sent out to the bus from the CPU board (and from the DMA controller is installed). The status lines consist of 8 lines which are selectively used by the memories and I/O boards to obtain information about the nature of the cycle. Those lines are also displayed on the front panel. The status lines are electrically of the same nature as the address lines, which means that they should be loaded by only one low power TTL or one low power Schottky TTL load per board. A DMA controller must be capable of generating these signals during a DMA transfer. These lines are SINTA-H, SWO-L, SSTACK-H, SHLTA-H, SOUT-H, SM1-H, SINP-H, and SMEMR-H.

The processor lines are a buffered group of inputs and outputs which are derivatives of the Intel 8080 processor signals. The 6 processor output lines are PSYNC-H. PDBIN-H. PWAIT-H. PWR-L. PHLDA-H, and PINTE-H. The DMA controller has control of these lines during a DMA transfer. The 5 input lines are PRDY-H, XRDY-H, PHOLD-L, PINT-L, and PRESET-L. Since some of the output signals in this group are used to drive front panel indicators, the input loading should not exceed one low power TTL or one low power Schottky TTL load per board. The input signals are all "pulled-up" using 1k Ohm resistors so that they may be driven by any Tri-state or open collector TTL gate or buffer. Although many kits (and the Altair manual itself) advocate the use of the PRDY-H line for inducing "wait" states, a much better and electrically correct) way of doing this is to use the XRDY-H line. The front panel drives PRDY-H with a constantly enabled 8T97 which has substantial haigh going drive capability. To pull this line down while the front panel is pulling it high causes large instantaneous surge currents in the devices, causing unnecessary noise spikes as well as abuse to the devices themselves.

The disable group of lines is used to disable the various Tri-state drivers on the CPU board when a DMA cycle occurs. The DMA controller then becomes responsible for driving the disabled lines. There are 4 disable signals which are used with DMA. They are STADSB-L, C/CDSB-L, ADDDSB -L, and DODSB-L. A fifth disable signal is SSWDSB-L, which has nothing to do with DMA, but instead is used to gate in the sense switches when an IN 377 (octal) instruction occurs.

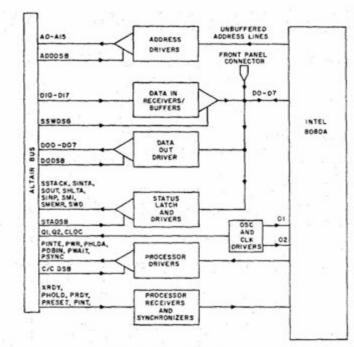

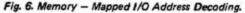

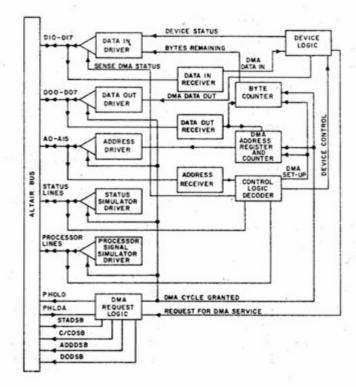

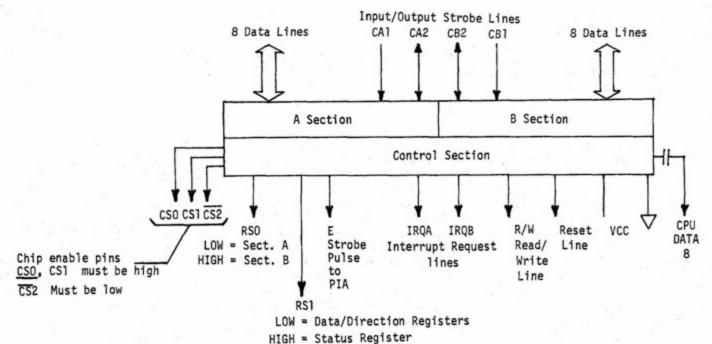

The heart of the Altair 8800 system is the CPU board. A block diagram of this board is shown in Fig. 1. This block diagram is provided to give an overview of the CPU connections to the bus. All references of in and out in the Altair system are with respect to the CPU board. The bidirectional data lines of the 8080 microprocessor are split into data-in and dataout lines for use on the Altair bus. The contents of the bidirectional data lines are latched into the 8212 latch at SYNC time by the O1 signal. The outputs of the 8212 latch are buffered for system use by 8T97 Tri-state buffers. The processor output signals are also buffered using 8T97s and

Fig. 1. CPU Block Diagram.

presented to the bus. The processor input signals are also buffered using 8T97s and presented to the bus. The processor input signals are passed through receivers and then presented to the 8080 chip. The ready signals (PRDY-H and XRDY-H) are ANDed, synchronized with Ø2, sent to the 8080. PHOLD-L is also synchronized with O2 before being sent to the 8080. The CPU block diagram should also be of value in the event that troubleshooting the CPU becomes necessary.

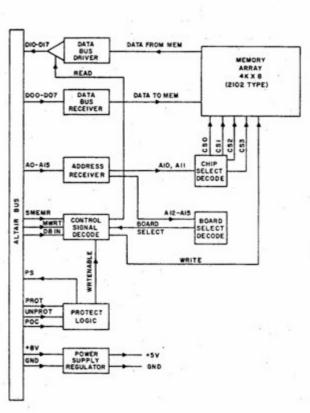

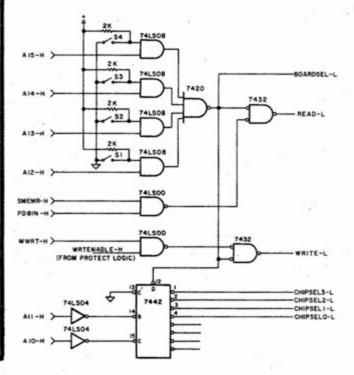

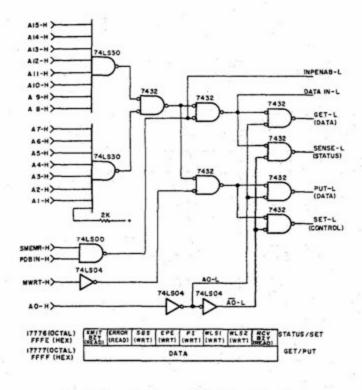

Fig. 2 is a block diagram of a typical 4K byte static memory as implemented for the Altair bus. In the static memory board, the control is relatively simple, with the major effort in the area of address decoding and control signal generation. Fig. 3 shows how this might be accomplished. The methods chosen for simplicity and are based on readily available, inexpensive components. S1 through S4 are address selection switches, which determine the position in the address range the board will occupy. These switches are normally of the DIP-SWITCH type, but may be replaced by jumpers for economy. BOARDSEL-L will be active (low) is all 4 switches match the state of the respective address lines associated with the switches. BOARDSEL-L has several functions, which include enabling the CHIPSEL decoder which is a 7442 decoder, providing an enabling input to both the READ-L and WRITE-L gates and finally in allowing the PROTECT flipflop (not shown) to be changed by either the PROT-L or UNPROT-L signals. The CHIPSEL decoder is connected so as to provide one of four chip selects according

to the state of A10-H and A11-H. Either READ-L or WRITE-L is produced during a memory cycle based on the state of SMEMR-H, PDBIN-H, and MWRT-H lines at the time BOARDSEL-L is low. WRITE-L is used as a memory write pulse and is fed to pin 3 of all the 2102 chips on the board during a memory write cycle. Only those 2102s selected by an active (low) CHIPSEL signal will be written into. READ-L is used to enable the DATA BUS DRIVER which is composed of 8T97 buffers feeding the datain lines. There are many ways to accomplish the address decoding other than as shown. Among these are the use of address comparator chips to produce BOARDSEL-L.

Keep in mind that the purpose of discussing the memory, CPU, and I/O interfaces is to give an insight into the Altair bus considerations for the boards, not to provide complete design details. With the information provided, it is hoped that you will be able to pick up the ball and make your own designs work. Also, many general designs shown in other articles may be adapted for your Altair, using the techniques in this article.

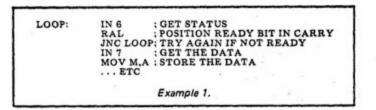

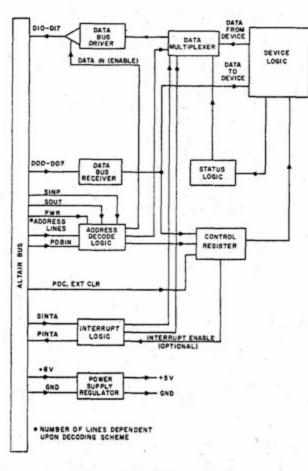

By far, the largest area open to hardware experimentation in the personal computer system is that of I/O interfacing. If you are started to design an I/O interface from scratch, the first order of business is the conceptual design. This first involved deciding what function the interface board will perform. Once the function has been defined, it must then be decided how the interface will **look** to your software. This is

continued

| #           | Mnemonic  | Description                                  |        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------|----------------------------------------------|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | + 8 Volts | Unregulated power supply for                 | 39     | DO5-H       | Data Out (from CPU) Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| '           |           | use by +5 Volt on-board reg-                 | 40     | D06-H       | Data Out (from CPU) Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 100         |           | ulators.                                     | 41     | D12-H       | Data In (to CPU) Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •           | +16 Volts | Unregulated power supply for                 | 42     | D13-H       | Data In (to CPU) Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2           | 110       | use by on-board regulators                   | 43     | D17-H       | Data In (to CPU) Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |           | (typically to obtain +12 Volts).             | 44     | SM1-H       | CPU status signal indicating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1           | XRDY-H    | A normally high line, which if               |        |             | processor is in machine cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3           |           | brought to the low state will                |        |             | 1 which is Instruction Fetch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |           | cause the CPU to enter the                   | 45     | SOUT-H      | CPU status signal indicating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |           | WAIT state.                                  |        |             | the current cycle is an Out-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | VIO-H     | Vectored Interrupt priority 0                |        |             | put cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4           | VII-H     | Vectored Interrupt priority 1                | 46     | SINP-H      | CPU status signal indicating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5<br>6<br>7 | VI2-H     | Vectored Interrupt priority 2                |        |             | the current cycle is an In-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7           | V13-H     | Vectored Interrupt priority 3                |        |             | put cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8           | VI4-H     | Vectored Interrupt priority 4                | 47     | SMEMR-H     | CPU status signal indicating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| °,          | VI5-H     | Vectored Interrupt priority 5                | 100    |             | the current cycle is a Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10          | VIG-H     | Vectored Interrupt priority 6                |        |             | Read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11          | V17-H     | Vectored Interrupt priority 7                | 48     | SHLTA-H     | CPU status signal indicating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12-17       | Not Used  | vectored interrupt priority /                |        | Different   | the CPU is Halted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18          | STADSB-L  | Causes the 8 status line buffers             | 49     | CLOC-L      | A buffered 2 MHz clock for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10          | STADSD-L  | on the CPU board to be Tri-                  |        | OLOO L      | general use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |           |                                              | 50     | GND         | System ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | *         | stated (enter the high imped-                | 51     | +8 Volts    | (Same as pin 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | O/ODOD I  | ance state).<br>Causes the 6 command/control | 52     | -16 Volts   | Unregulated negative power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19          | C/CDSB-L  | line buffers on the CPU board                |        | -10 101(5   | supply for use by on-board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |           |                                              |        |             | regulators (typically to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |           | to be Tri-stated (enter the                  |        |             | obtain -5 Volts or -12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | INFRATIL  | high impedance state).                       |        |             | Volts).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20          | UNPROT-H  | A signal which is ANDed with                 | 53     | SSWDSB-L    | "Sense Switch Disable" which                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |